Biography

I’m a digital IC design engineer with a strong focus on ASIC, CPU architecture, RTL, and SoC.

My experience spans RISC-V SoC tape-out on TSMC 65nm (Apple Inc. sponsored), a 3-way Out-of-Order (OoO) R10K processor, and RTL implementation of FIR filters and CNN accelerators. I’ve also worked on VLIW-based TPU design during my 2025 summer internship at Zhonghao Xinying Technology Co., Ltd. (Taize Semiconductor R&D Center), extending ISA and building vector/scalar functional units.

Let’s connect! 📧 yuan0minor3@gmail.com | yj2848@columbia.edu

- Digital IC

- ASIC

- CPU Architecture

- RTL Design

- SoC

- Design Verification

- Embedded AI

M.S., Electrical Engineering, Expect Dec 2025

Columbia University

B.S., Electrical Engineering, May 2024

University of Minnesota, Twin Cities

B.S., Computer Engineering, May 2024

University of Minnesota, Twin Cities

B.A., Computer Science, May 2024

University of Minnesota, Twin Cities

Highlights

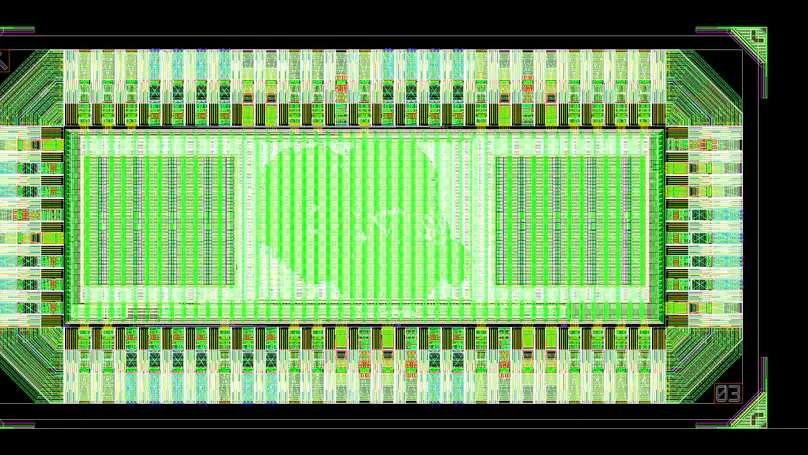

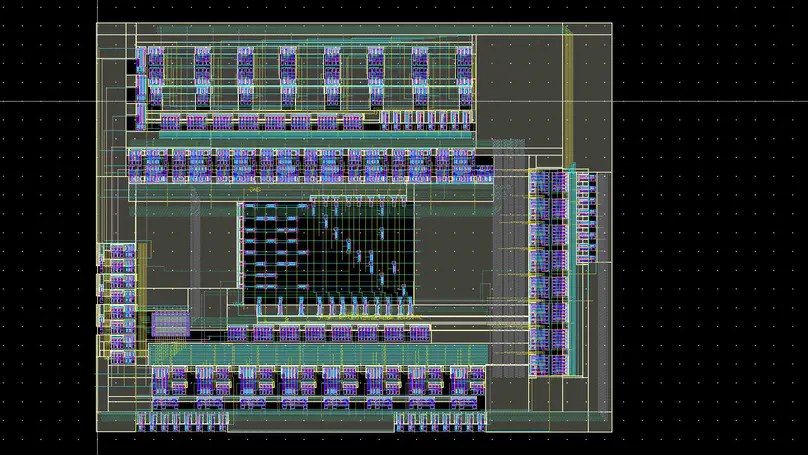

This project taped out a 2 mm² 32-bit RISC-V processor SoC based on OpenHW Group’s CV32E40P RTL using TSMC 65nm technology, operating at 200 MHz with 2.177 mW total power. It Integrated SPI, UART, I2C, GPIO, AXI/AHB buses, clock generator, scan chain, and custom 2-port SRAMs.

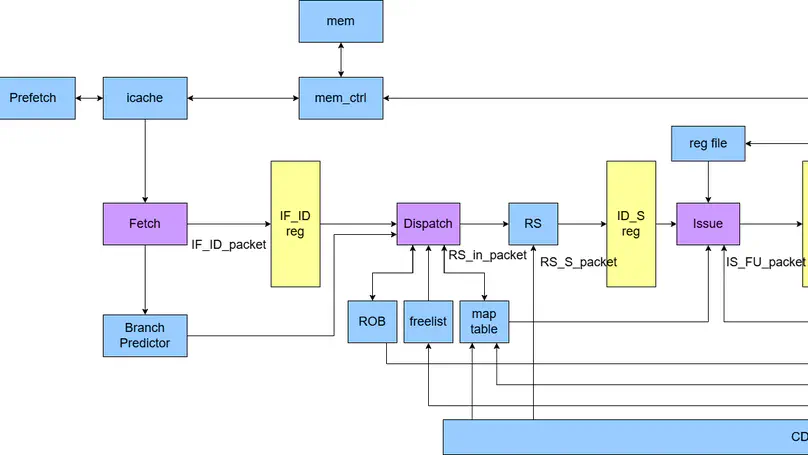

An out-of-order, 32-bit processor based on a 3-way scaled R10K microarchitecture which supports the RV32IM ISA.

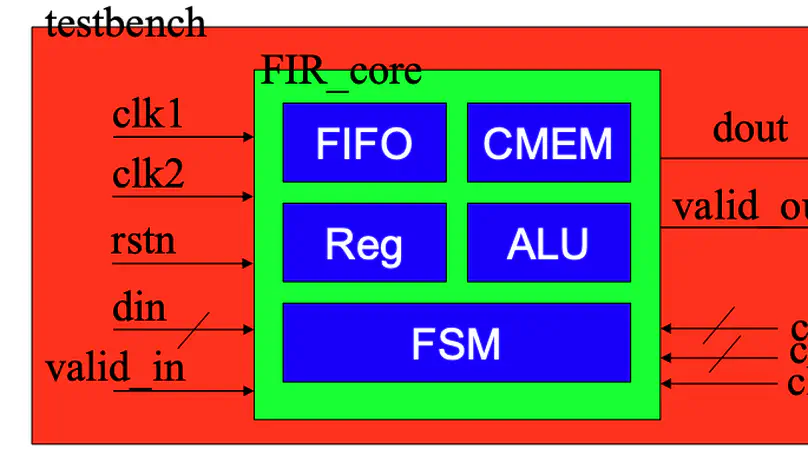

Designed and verified a 64-tap, 16-bit dual-clock FIR filter in Verilog RTL, achieving IEEE754 FP16 compliance, high energy efficiency (0.549 pJ/S), and 99.92% accuracy through synthesis, simulation, and back-annotation on IBM 130nm CMOS technology.

Architected and validated an 8-bit microprocessor in Cadence Virtuoso, achieving a compact 0.0149 mm² layout with DRC/LVS clean results and a critical path delay of 137 ps.

Experience

- Extended ISA for a VLIW-based TPU acceleration cores in SystemVerilog to support scalar and vector arithmetic instructions, including signed/unsigned integer operations, BF16/FP32 computation, and AI inference instructions such as matrix transpose and ReLU.

- Architected a Tomasulo hazard resolution (register renaming) unit to replace Scoreboard, eliminating data hazards (RAW/WAW) and deadlocks.

- Contributed to pipeline RTL verification and developed UVM components (driver, monitor, scoreboard) to validate ISA extensions, instruction formats, functional units, and pipeline correctness under hazard and dependency conditions.

- Co-designed PCBs integrating STM32 and RISC-V CH32V chips to support multiple protocols (Modbus RTU, UART, CAN).

- Optimized bus transmission stability by designing DMA allocation and auto-baud rate calculation using C on RT-Thread.

- Engineered Python-based Qt5 UI software with LubanCat-Zero board, decreasing communication analysis time by 80%.

- Participated in organizing academic or company info sessions.

- Managed onboarding for prospective HKN members.

Summer Research & Senior Honors Project

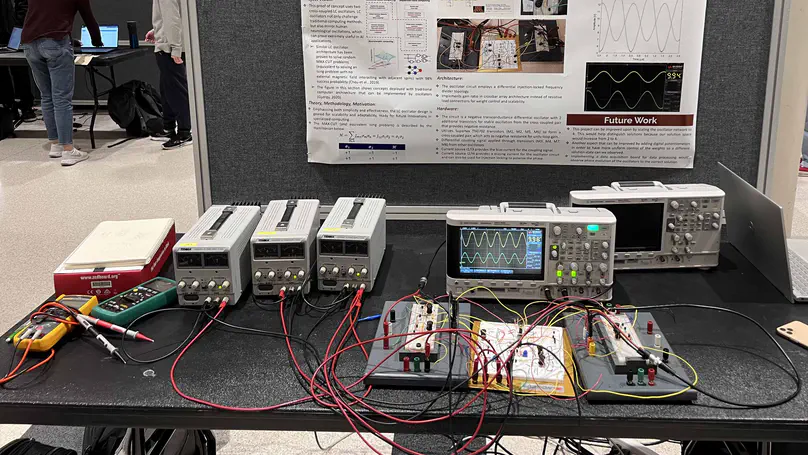

- Developed a test system (Senior Honor Capstone) for a 48-node Coupled Oscillator Based Ising (COBI) Solver Chip.

- Designed 3 high-speed PCBs for COBI chips by Altium Designer to ensure connectivity and reduce energy consumption by 30%.

- Extended the Raspberry Pi-based interface using Python to analyze Hamming distance (HD) for higher solution quality.

- Set up a FPGA board PCIe with FMC+ slot (AMD/Xilinx Kintex-7) to facilitate efficient data transfer from chips.

- Created the Verilog/HDL and C program to measure and compare large-scale optimization problem solution accuracy.

- Hold weekly office hours tutoring in Electrical or Computer Engineering core courses.

- Offered peer advising services for ECE students in classes and specializations.

Undergraduate Research Opportunities Program (UROP)

- Explored impact of geometrical constraints of DNA-like materials on chiral-induced spin selectivity (CISS) effect.

- Collaborated 2 research associates to simulated numerically quantum spin transport in chiral DNA-like molecules in MATLAB.

- Organized and assessed data on Origin to validate the numerical approach and provided a comprehensive report.

- Provided academic tutoring to freshmen in physics, calculus and chemistry in both entry and advanced levels.

- Attended and actively participate in scheduled training sessions and staff meetings.

Project

- Taped out a 2 mm² 32-bit RISC-V processor SoC based on OpenHW Group’s CV32E40P RTL using TSMC 65nm technology, operating at 200 MHz with 2.177 mW total power. Integrated SPI, UART, I2C, GPIO, AXI/AHB buses, clock generator, scan chain, and custom 2-port SRAMs.

- Implemented Harvard architecture with dual 16KiB Instruction/Data caches using SRAM macros, completing RTL to GDSII flow including UVM verification, placement & routing (PnR), static timing analysis (STA), DRC/LVS, and post-layout simulation.

- Built a custom PCB and developed C/RTL co-simulation framework for post-silicon validation, enabling register tests, peripheral loopback, and memory interface verification.

- Designed a 32-bit 3-way superscalar out-of-order processor in SystemVerilog, supporting the RV32IM ISA and speculative execution with checkpoint recovery. Achieved CPI 2.826 with a minimum 11.2 ns clock period, delivering 1.77× speedup over a 5-stage in-order baseline.

- Featured 64-entry register renaming, 16-entry RS, 32-entry ROB, and parallel functional units (3 ALUs, 2 Loads, 2 Multipliers, 1 Branch). Implemented an 8-entry Load-Store Queue (LSQ) with store-to-load forwarding and hazard resolution. Integrated a hybrid Tournament branch predictor (Gshare + Bimodal) to reduce CPI from 3.7 to 2.8.

- Developed non-blocking 256B Instruction/Data caches with write-back and write-allocate policies. D-cache is 2-way set-associative with LRU replacement and MSHRs. I-cache is 32-line direct-mapped with a 12-line branch-aware prefetcher to reduce fetch stalls.

- Smart Waste Advisor is a self-contained embedded system that performs real-time object classification and delivers disposal tips via on-device display and audio. It uses a MobileNetV1 model for classification and integrates OpenAI GPT-3.5 Turbo for natural language feedback.

- This project explores how smart contract event data can be extracted from the Ethereum blockchain and used to enable meaningful analysis with large language models (LLMs). We focus on OpenSea’s Seaport contract, indexing NFT sales events using The Graph Protocol, processing the results with Python, and generating structured data for NFT market trend prediction.

- Implemented a 64-tap, 16-bit FIR filter in Verilog RTL, utilizing a dual-clock system with a 10 kHz input clock and a processing clock of up to 34.03 MHz, delivering a throughput of 10 kS/s while compliant with IEEE754 FP16 standards.

- Developed a robust architecture incorporating FSM control, dual-clock FIFO synchronization, and an ALU for MAC operations and FX-to-FP conversion, along with a single-port SRAM block generated by memory compiler and a 64-depth shift register.

- Synthesized the design using Synopsys Design Compiler on IBM 130nm CMOS technology with PPA optimization, achieving a total cell area of 86547.7 mm² with no timing violations. Post-synthesis analysis with Synopsys PrimeTime measured power consumption at 1.868 × 10⁻⁵ W and energy efficiency of 0.549 pJ/S.

- Validated functionality through QuestaSim waveform simulations and gate-level SDF back-annotation, achieving 99.92% average accuracy compared to MATLAB golden outputs using NRMSE metrics.

- Designed and integrated a SystemC-based CNN accelerator into a 2×3 ESP SoC platform featuring Ariane/Leon3 core, memory, cache, and NoC, with AXI4 and a 32-bit DMA controller for interfacing. Achieved 10x latency and 5x performance improvements through ping-pong buffering and partitioned local memory (PLM), and verified functional correctness at both module and system levels.

- Synthesized the accelerator with Catapult HLS using pipelining and loop unrolling, deployed it on Xilinx VC707 FPGA for hardware validation, Pareto-optimal analysis and debugged DMA behavior, memory mapping, and cache coherence issues.

- Architected an 8-bit microprocessor core in Cadence Virtuoso, integrating components such as an adder, logic shifter, PLA, latch, MUX, 8x8 SRAM, bus driver and accumulator, emphasizing transistor-level design, functionality, and layout optimization.

- Verified functionality and instruction set execution through Spectre simulations, achieving a compact 0.0149 mm² layout with DRC/LVS clean results and a critical path delay of 137 ps.

- Designed a two-stage operational transconductance amplifier (OTA) with Miller compensation at the transistor level, including schematic design and simulation.

- Achieved key performance metrics: 0.1% measurement error, 651 µA total current consumption (±1.5 V voltage supply), 60 dB loop gain, 80° phase margin, and 10.53 MHz closed-loop bandwidth.

- Achieved a coupled oscillator system to solve two-space Ising optimization problems by analyzing output phase differences.

- Simulated and built LC oscillators by LTspice optimizing biasing current to achieve desired frequency and amplitude.

- Improved physical circuit by switching from Constant Current Load (CCL) to current mirror, reducing heat generation by 90%.

- Designed the circuit with a differential injection-locked frequency divider topology integrating Supertex TN0702 transistors, current sources, and amplifiers for precise control and scalability.

- Created an optimization tool in C++ inspired by FastPlace Algorithm focusing on IC placement challenges.

- Engineered features including parsing IBM benchmarking files, applying global optimization via conjugate gradient, cell spreading, and force addition techniques to reduce overlaps, with visual outputs by Python.

- Developed an STA engine in C++ handling logical circuits in industry-standard benchmark models like ISCAS'85, ‘89, and ITC99.

- Utilized NLDM-based Look-Up Tables (LUTs) for computation of metrics such as delay, worst slack, slew, and load capacitance.

- Employed topological traversal techniques to identify critical paths, ensuring comprehensive analysis of circuit timing.

- Revised the resolution of 10-bit ADC on the Microchip PIC24 microcontroller to 14-bit within 10% error.

- Executed oversampling and averaging to enhance SNR and effective resolution of converted signal.

- Built PCB on Altium Designer and packaged circuit board in a Bud 750-1015 enclosure with I/O and LCD display.

- Led 4-member team and wrote a C program to control a fan to turn on/off automatically at a certain temperature.

- Deployed I2C protocol to read data through temperature sensor and showed temperature value in an LCD display.

- Allowed user to press button to send PWM signals to motor driver which changes the fan’s speed.

- Explored the impact of geometrical constraints of DNA-like materials on the chiral-induced spin selectivity effect.

- Used fundamentals, theoretical and experimental reports, numerical methods to solve problem that how does the geometrical length of DNA-like materials affect the amount of spin filtering by CISS.

- Reproduced literature results with in-house Matlab code to validate the numerical approach.

- Collaborated with research associate to find the optimal geometrical factor of the DNA-like materials.

- Analyzed the results with physics principles, reported writing and prepared a presentation.

- Wrote Java to create a board game that allows 2 users to take turns to play and defined several game objects in class: Board, Cell, Boat, and Game; implemented Debug mode to perform end-to-end testing and bug tracing.

- Wrote Python to create a game to control a lander that descending toward the moon at a slow enough speed.

- Simulated gravity to accelerate the craft towards the moon’s surface and simulated the falling meteors in the environment.

- Added controls for thrust, which accelerates the craft in the direction it’s currently facing, and turning, which adjusts the orientation of the craft to the left or right.

Volunteer

2023 Commencement Event:

- Assisted with steaming and prepping Regalia and other supplies for Stage Crossings.

- Provided assistance with setup in the backstage and stadium field areas.

- Assisted students after check-in, answered questions, and addressed any last-minute needs.

- Ensured that students remain in defined lines for the processional.

- Indicated to students when to start processing and made sure they remain in lines.