64-Tap 16-bit Dual-Clock Fixed-to-Floating-Point FIR Filter Design Based on IBM 130nm CMOS Technology

Abstract

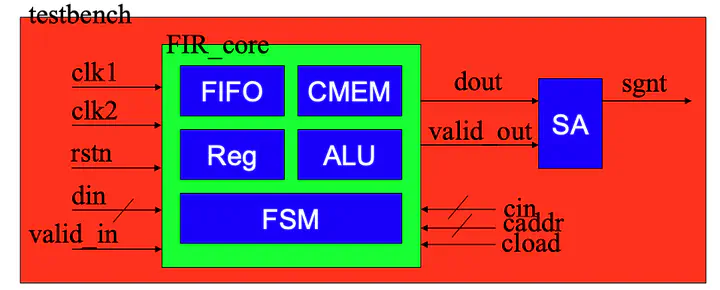

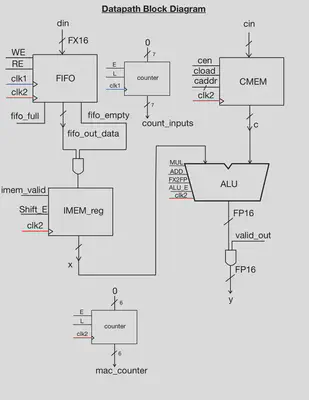

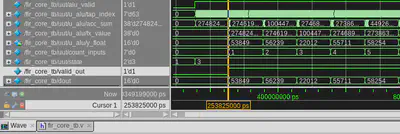

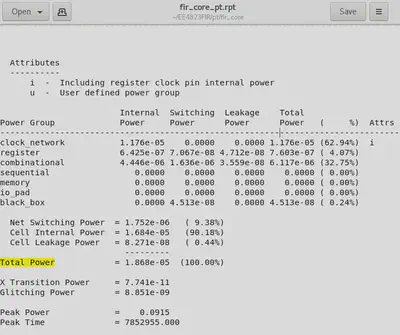

This project presents the design and realization of a 64-tap, 16-bit Fixed-to-Floating-Point Finite Impulse Response (FIR) filter by implementing in Verilog RTL. The design operates with a 10 kHz input clock and a high-performance processing clock of up to 34.03 MHz, delivering a throughput of 10 kS/s while fully compliant with IEEE754 FP16 standards. At the core of the architecture is an intricate integration of FSM-driven control, asynchronous FIFO, and a purpose-built Arithmetic Logic Unit (ALU) enabling efficient MAC operations and FX-to-FP conversion. Supporting these operations, the system incorporates a single-port SRAM memory block generated by memory complier and a 64-depth shift register. The filter was synthesized on IBM 130nm CMOS technology using Synopsys Design Compiler, achieving Pareto-optimal power, performance, and area metrics, with a total cell area of 86547.7 mm² and no timing violations. Detailed post-synthesis analysis conducted in Synopsys PrimeTime quantified a minimal power consumption of 1.868 × 10⁻⁵ W and exceptional energy efficiency of 0.549 pJ/S. Rigorous validation through QuestaSim waveform simulations and gate-level SDF back-annotation demonstrated a remarkable 99.92% accuracy against MATLAB golden outputs.

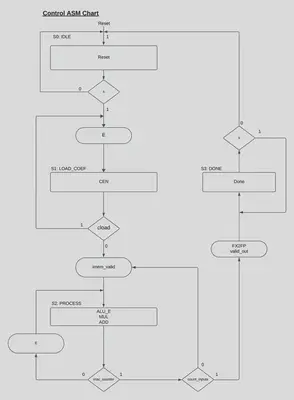

DESIGN METHODOLOGY

ASM Chart:

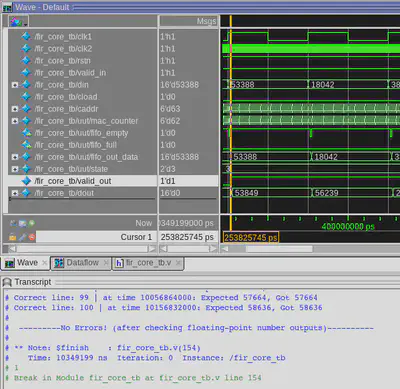

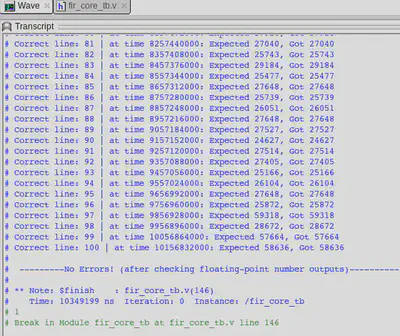

SIMULATION

Functional verification:

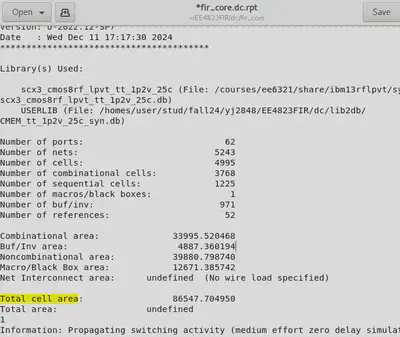

METRICS

Total Cell Area:

Links

Please find more details in Github, Final Report, and Slides.