8-bit Microprocessor Design Based on TSMC 65nm CMOS Technology

Abstract

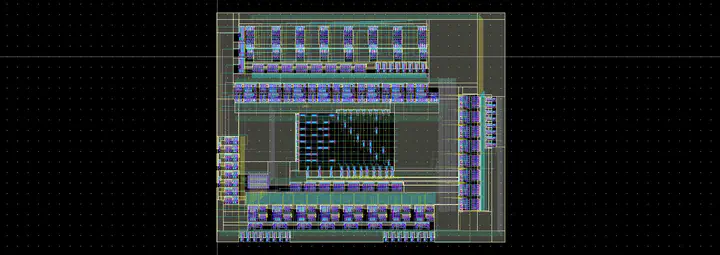

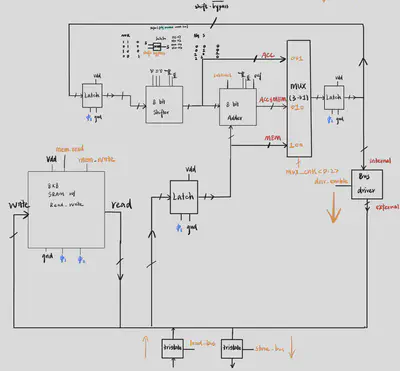

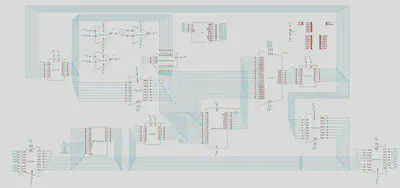

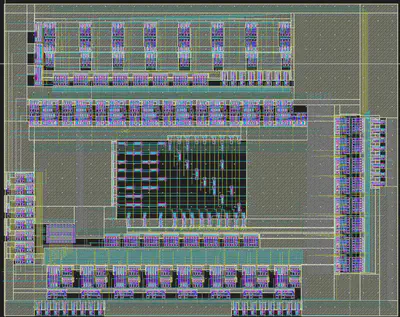

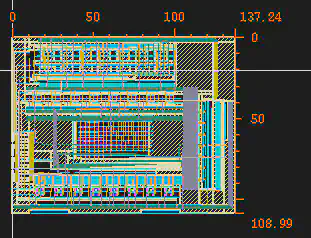

This project focuses on the design and implementation of an 8-bit microprocessor using TSMC 65nm CMOS technology. The microprocessor was developed at the transistor level with key components, including a ripple carry adder, logic shifter, multiplexer, 8x8 SRAM, PLA, latch, bus driver, and accumulator. Schematic design, logic functionality, sizing, and layout optimization were conducted using Cadence Virtuoso, achieving a compact chip area of 0.0149 mm² and a critical path delay of 137 ps. The design integrates functional dataflow units, register files, and memory to support reliable instruction execution. Clock cycle timing was simulated with Spectre to ensure functional correctness and latency optimization. The layout was validated with Design Rule Check (DRC) and Layout Versus Schematic (LVS) verification.

Datapath

Schematic and Layout

MPU Schematic:

Simulation Example (Subtraction)

Links

Please find more details in Final Report, Reference.