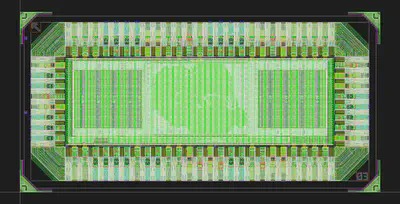

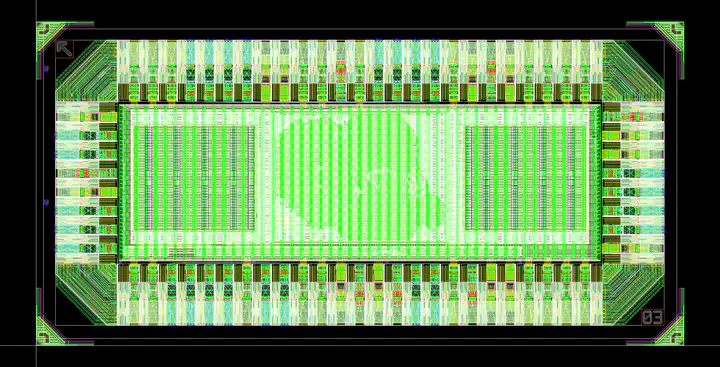

4-Stage RISC-V Processor SoC Design & Tape-Out (Apple Inc. Sponsored)

Abstract

This project taped out a 2 mm² 32-bit RISC-V processor SoC based on OpenHW Group’s CV32E40P RTL using TSMC 65nm technology, operating at 200 MHz with 2.177 mW total power. It Integrated SPI, UART, I2C, GPIO, AXI/AHB buses, clock generator, scan chain, and custom 2-port SRAMs.